同步時序原理是數(shù)字集成電路設(shè)計中的核心概念之一,尤其在信息系統(tǒng)集成和物聯(lián)網(wǎng)技術(shù)服務(wù)中應(yīng)用廣泛。同步時序電路通過統(tǒng)一的時鐘信號來控制所有存儲元件(如觸發(fā)器或寄存器)的狀態(tài)更新,確保數(shù)據(jù)在系統(tǒng)中以同步方式傳輸和處理,從而避免競爭和冒險現(xiàn)象,提高系統(tǒng)穩(wěn)定性和可靠性。

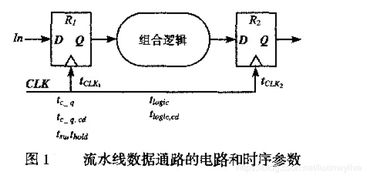

在同步時序電路中,時鐘信號決定了時序操作的節(jié)奏。每個存儲元件在時鐘的有效邊沿(如上升沿或下降沿)采樣輸入數(shù)據(jù),并更新輸出狀態(tài)。這種機制消除了異步電路中因信號傳播延遲不一致而可能引發(fā)的錯誤。同步設(shè)計還簡化了時序分析,例如建立時間和保持時間的檢查,確保電路在指定時鐘頻率下正常工作。

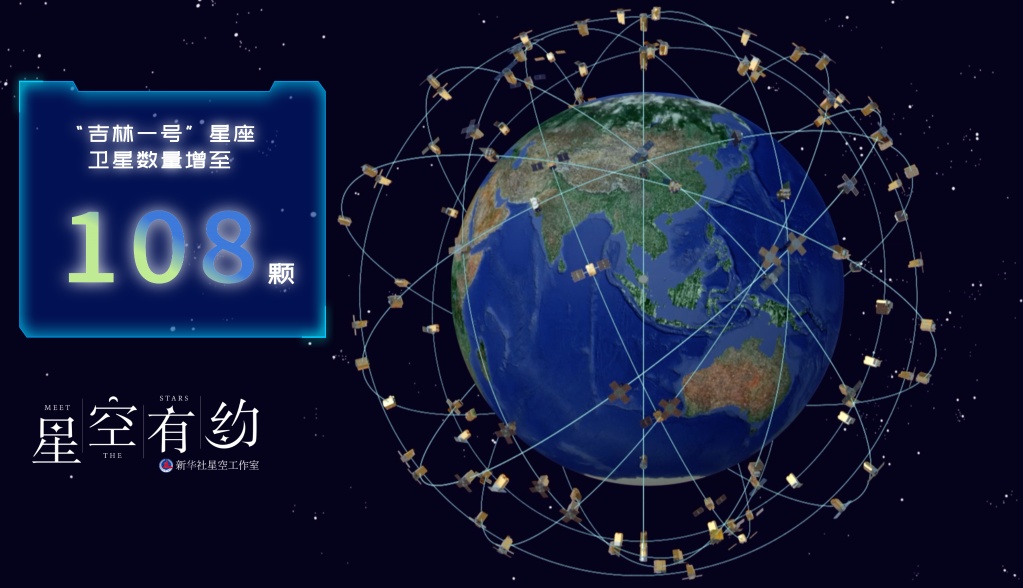

同步時序原理在信息系統(tǒng)集成中尤為重要,例如在處理器、存儲控制器和通信接口中,它保證了多模塊間的協(xié)調(diào)運行。在物聯(lián)網(wǎng)技術(shù)服務(wù)中,同步時序用于傳感器數(shù)據(jù)采集、邊緣計算設(shè)備和網(wǎng)絡(luò)協(xié)議處理,確保實時性和數(shù)據(jù)一致性。通過合理設(shè)計時鐘分布和時序約束,工程師可以優(yōu)化功耗、性能和面積,滿足復(fù)雜應(yīng)用的需求。